キャッシュメモリとは:L1, L2, L3の違い・キャッシュヒット率

キャッシュメモリとは

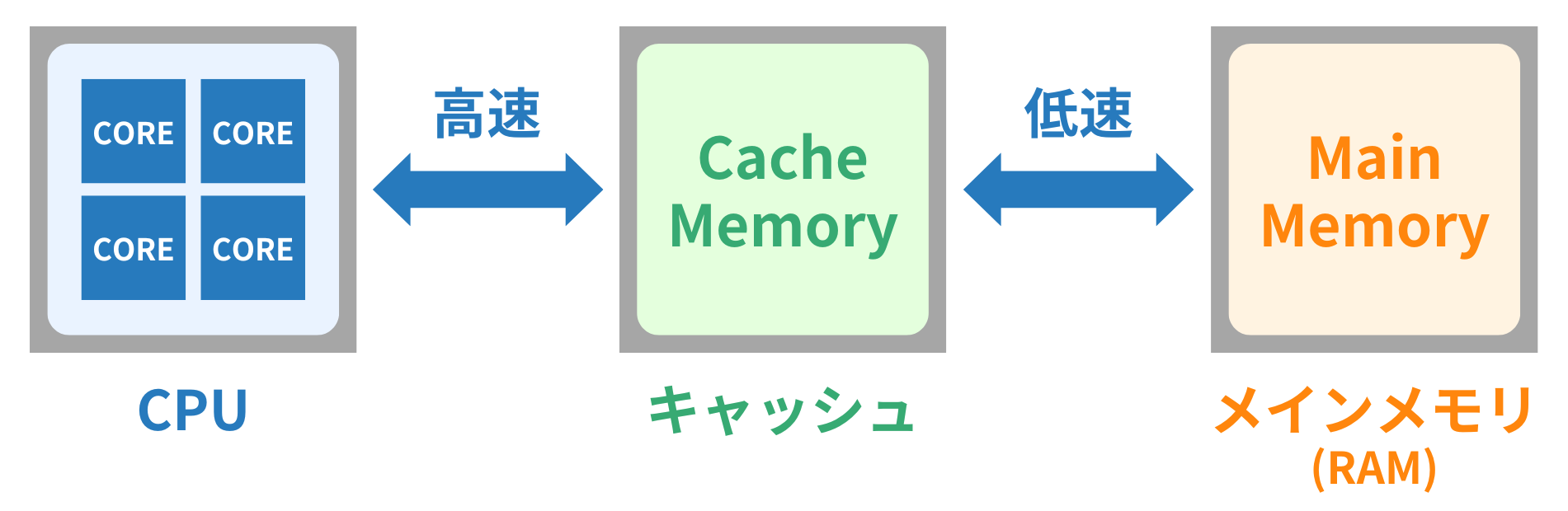

キャッシュメモリは「CPU内にある高速な記憶装置(メモリー)」です。CPUが頻繁に使うデータや命令を一時的に保存し、すぐにアクセスできるようにすることで、処理速度を向上させます。

通常、CPUが処理する命令やデータは、CPU外のメモリー(RAM, 主記憶装置)に保存されています。主記憶装置(RAM)は大容量ですが、CPUと比べるとアクセス速度が遅いため、CPUが必要な命令やデータを毎回RAMから取得すると、処理速度が低下してしまいます。そこで活躍するのがキャッシュメモリです。

キャッシュメモリには、SRAM(Static RAM)という種類のメモリが使われています。一般的なRAM(DRAM:Dynamic RAM)と比べて、高速ですが容量が小さく、コストも高くなります。そのため、CPUの近くに小容量・高速なキャッシュメモリを配置し、頻繁に使うデータを素早く読み込めるようにすることで、処理速度を向上させています。

CPUとは:コア数・スレッド数・動作周波数・キャッシュメモリ

階層構造:L1, L2 L3の違い

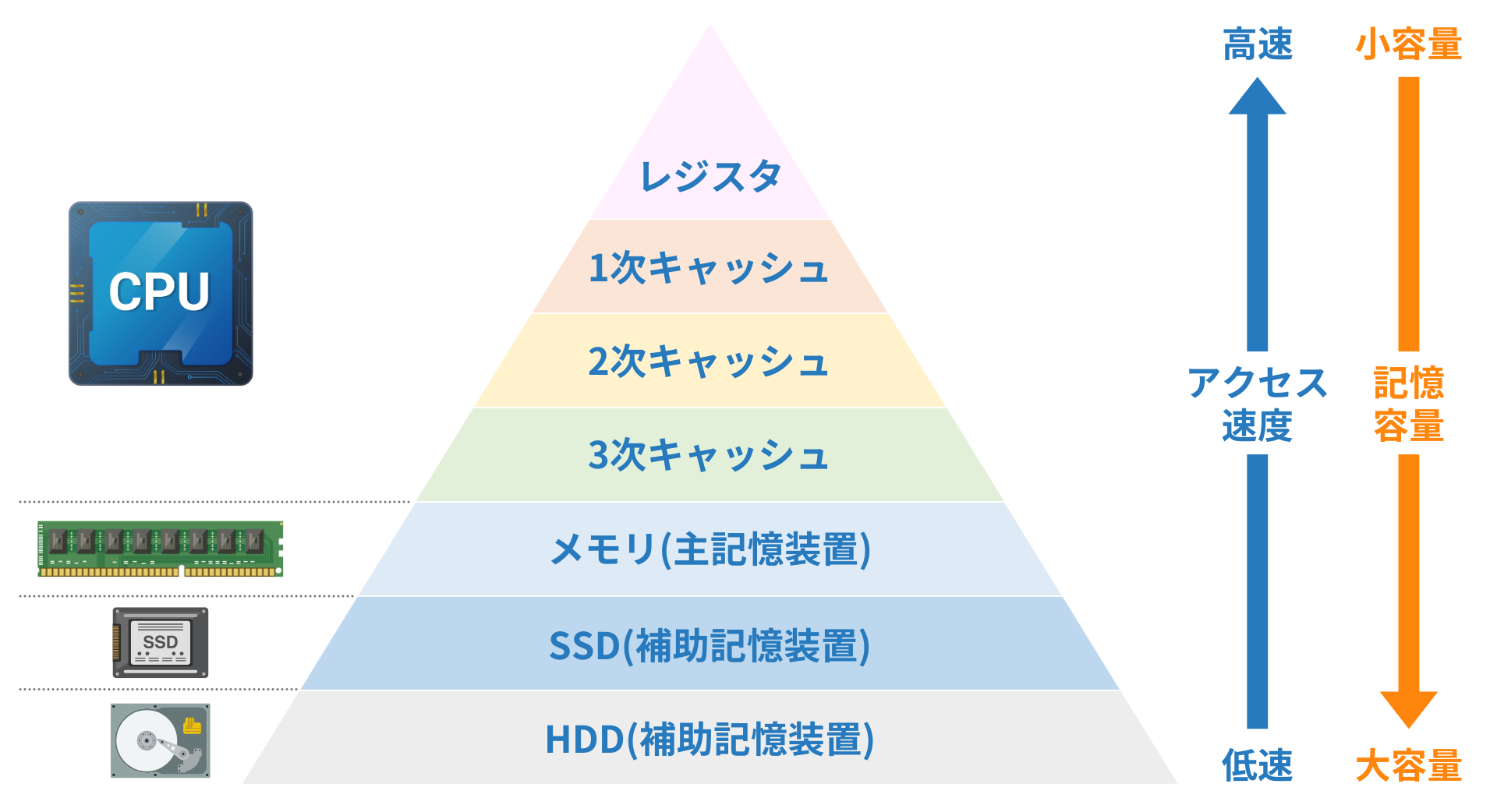

コンピュータのメモリ(記憶装置)には、レジスタ、キャッシュ、RAM、SSD、HDDなど、役割や速度、容量が異なる複数の階層があります。レジスタやキャッシュは高速で小容量、SSDやHDDは遅くて大容量です。それぞれのメモリは、CPUとデータのやりとりをサポートしています。

その中でもキャッシュメモリは、CPUに近い順にL1、L2、L3と分かれており、それぞれの階層がデータアクセスの効率を高め、CPUの性能を向上させます。

CPUの処理速度が向上するにつれて、メモリの高速化も求められるようになりました。しかし、高速である一方で高コストなSRAM構造の「キャッシュメモリ」を効率的に利用するために、1次(L1)、2次(L2)、3次(L3)キャッシュという階層構造が導入されました。CPUに近いほど小容量で高速なメモリが使われ、容量が不足すると、次第に低速だが容量が大きいメモリにアクセスする仕組みがCPU内に組み込まれています。

- L1キャッシュ(1次キャッシュ)

- L2キャッシュ(2次キャッシュ)

- L3キャッシュ(3次キャッシュ)

最も高速で、CPUコアに直接内蔵されており、小容量ですが、最も頻繁に使用されるデータを保持します。

L1よりやや遅いが、容量が大きく、複数のCPUコアで共有されることもあります。

L2よりもさらに大容量で、複数のCPUコア間で共有されるが、アクセス速度はL1やL2に比べて遅いです。

キャッシュメモリに階層構造を用いることで、コストを抑えながら、CPUは必要なデータに迅速にアクセスでき、処理速度を最大限に引き出すことができます。

DRAMとSRAMの違い

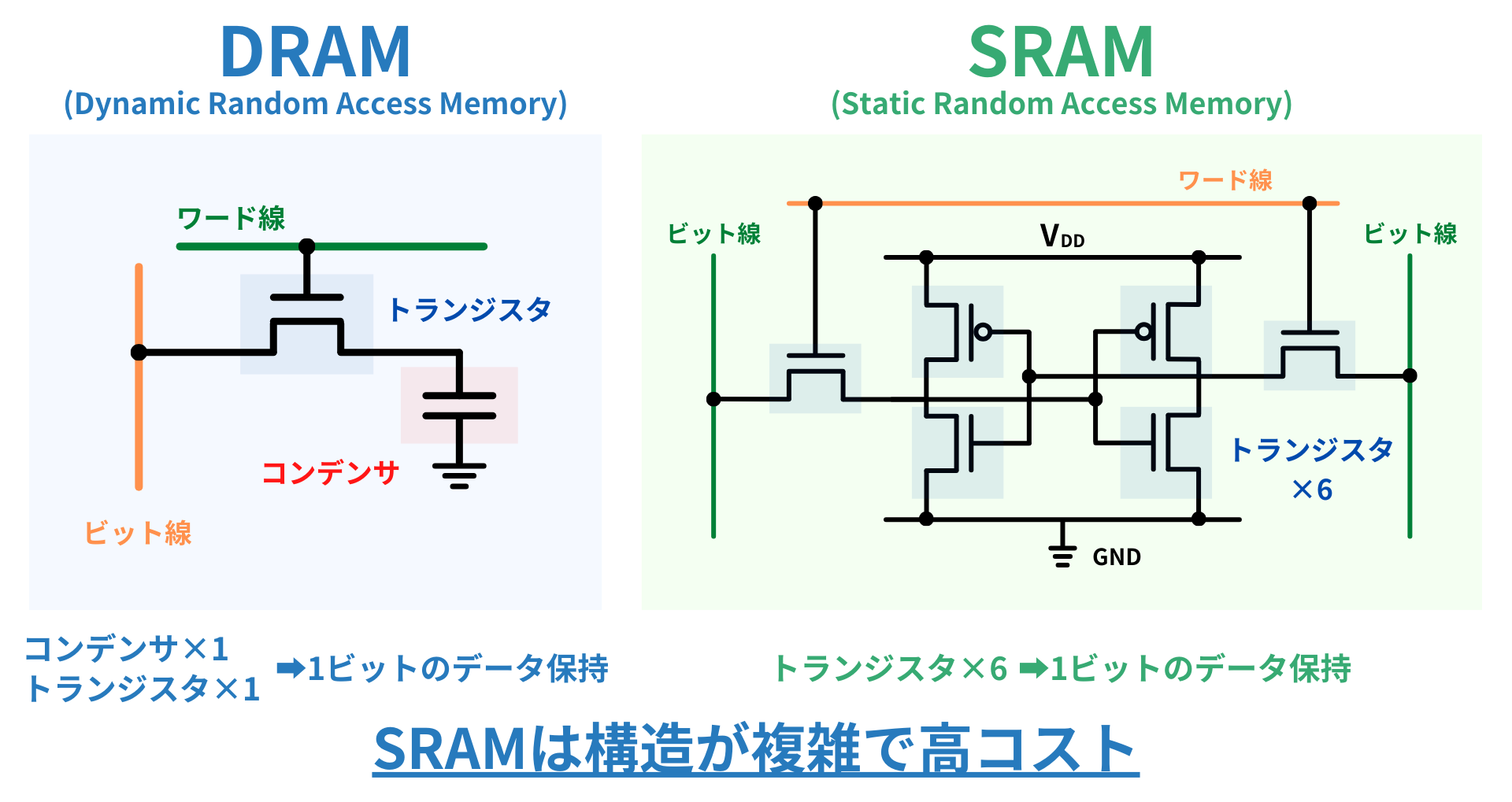

前述のように、キャッシュメモリにはSRAMが使われ、メインメモリにはDRAMが使われています。それぞれの特徴は以下の通りです:

- キャッシュメモリ:SRAMを使用するため、高速であるが、高コスト

- メインメモリ:DRAMを使用するため、低速であるが、低コスト

SRAMが高コストである理由は、デバイスの構造にあります。

SRAMはデータを保持するために、より多くのトランジスタを使用し、回路が複雑です。そのため、製造コストが高くなります。

- DRAM (Dynamic Random Access Memory)

- SRAM (Static Random Access Memory)

1つのトランジスタと1つのコンデンサで構成され、大容量化が容易で低コストですが、データ保持には定期的なリフレッシュが必要で、動作速度は遅くなります。

6つのトランジスタを使用し、構造が複雑で高コストですが、リフレッシュ不要で高速動作、低消費電力です。

SRAMは高速でありながら高コストのため、限られた容量を効率的に活用することが重要です。そのため、CPU内部では、性能向上のために階層構造を取り入れ、適材適所で使われているのです。

キャッシュヒット率とは

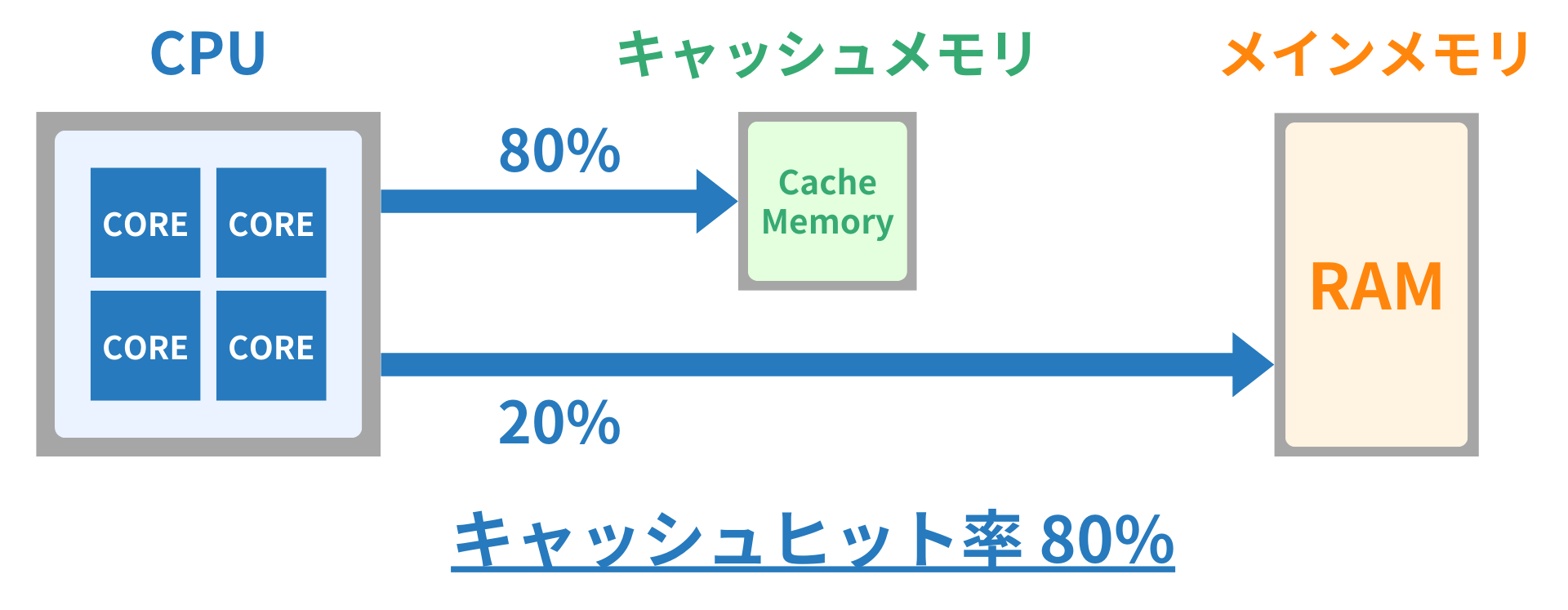

キャッシュメモリは高速ですが容量が限られているため、CPUが頻繁に使うデータを優先的に保持します。しかし、すべてのデータを収められるわけではなく、必要なデータがキャッシュに存在しない場合はメインメモリから読み込む必要があります。

「CPUが必要とするデータがキャッシュメモリに存在する確率」をキャッシュヒット率(Cache Hit Rate)と呼びます。キャッシュヒット率が高いほど、CPUは低速なRAMへのアクセスを減らせるため、処理速度が向上します。

キャッシュヒット率は以下の計算式で表されます。

ここで、キャッシュミス(Cache Miss)とは「CPUが必要なデータがキャッシュメモリにない状態」です。キャッシュミスが発生すると、データの取得に時間がかかり、結果としてCPUの処理速度が低下します。なお、キャッシュミス率は「1-キャッシュヒット率」で計算できます。

プリフェッチ

キャッシュミスが発生すると、CPUは低速なRAMへのアクセスが必要となり、処理速度が低下します。ここで活躍するのが「プリフェッチ」という技術です。

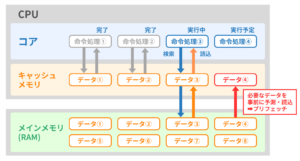

(出典:徹底図解 パソコンのしくみ 新版を基に筆者作成)

プリフェッチ(Prefetch)とは「PUが将来必要になりそうなデータを事前に予測し、あらかじめキャッシュメモリに読み込んでおく技術」です。

例えば、CPUが「処理1 → 処理2 → 処理3 → 処理4」と順番に命令を処理し、それぞれに必要なデータをデータ1~4とします。CPUは各処理の際にキャッシュメモリを参照し、必要なデータがあればすぐに利用できます(キャッシュヒット)。しかし、例えばデータ4がキャッシュにない場合、処理4の際にRAMへアクセスする必要があり、処理が遅くなります(キャッシュミス)。

プリフェッチは、処理とデータの規則性から、あらかじめRAMからキャッシュにデータを読み込む技術です。上図の場合、データ4をあらかじめ読み込んでおくことに相当します。プリフェッチを行うことにより、キャッシュミスを減らし、メモリアクセスの遅延を抑えて処理速度を向上させることができます。プリフェッチは、CPUの動作パターンやプログラムの実行順序を基に予測され、ハードウェア(ハードウェアプリフェッチ)やソフトウェア(ソフトウェアプリフェッチ)によって実行される場合があります。